TechWeb 文 / 新喀鸦

在 2021 年时,英特尔公司 CEO 帕特·基辛格曾表示:“基于英特尔在先进封装领域毋庸置疑的领先性,我们正在加快制程工艺创新的路线图,以确保到 2025 年制程性能再度领先业界。”而在最近,英特尔更新了制程路线图,包括 Intel 14A 制程技术、专业节点的演化版本,及全新的英特尔代工先进系统封装及测试(Intel Foundry Advanced System Assembly and Test)能力。那么英特尔的翻盘时间要到了吗?

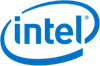

制程路线图

英特尔在本次更新的路线图中新增了 Intel 14A 和数个专业节点的演化版本。英特尔还证实,其“四年五个制程节点”路线图仍在稳步推进,并将在业内率先提供背面供电解决方案。英特尔预计将于 2025 年通过 Intel 18A 制程节点重获制程领先性。

对于演化版本,其型号后缀一般包含“E”、“P”或者“T”。其中:

E 代表功能扩展(Feature Extension)

P 代表性能提升(Performance Improvement)

T 代表用于 3D 堆叠的硅通孔技术(Through-Silicon Vias)

此外,英特尔代工还宣布将 FCBGA 2D+ 纳入英特尔代工先进系统封装及测试(Intel Foundry ASAT)的技术组合之中。这一组合将包括 FCBGA 2D、FCBGA 2D+、EMIB、Foveros 和 Foveros Direct 技术。

FCBGA 2D/2D+:倒装芯片球栅阵列(FC-BGA)是比较成熟的封装工艺,英特尔自 2016 年就进入大批量生产阶段(HVM)。拥有最大的先进热压缩键合(TCB)工具和设备库,具有很好的良率表现;

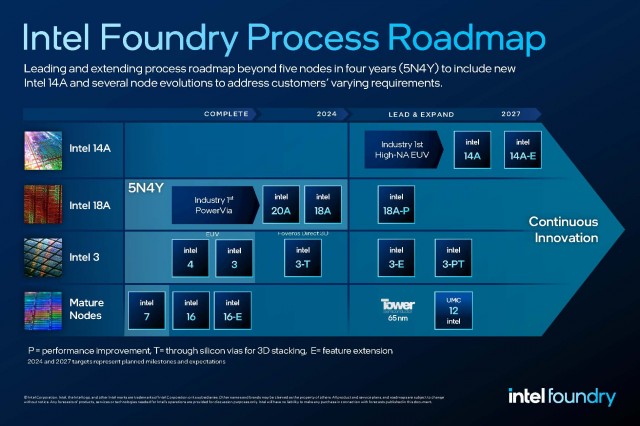

EMIB 2.5D:嵌入式多芯片互联桥接(EMIB)技术是一种埋入传统有机衬底的 2.5D 封装工艺,适合逻辑-逻辑芯片或逻辑-HBM 存储芯片的互联封装,2017 年开始批量生产;

Foveros 2.5D & 3D:Foveros 是一种裸片堆叠封装技术,适合 PC 和边缘处理器芯片的封装设计,2019 年开始量产;

EMIB 3.5D:结合 EMIB 和 Foveros(即原来的 Co-EMIB),适合多个裸片的 3D 堆叠封装,Intel 数据中心 GPU MAX 系列 SoC 即采用这种 3.5D 封装;

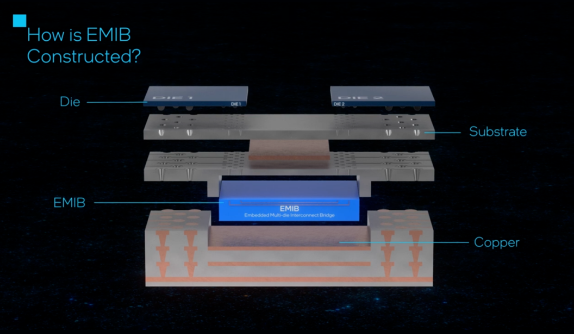

Foveros Direct 3D: Foveros Direct 使用了铜与铜的混合键合取代了会影响数据传输速度的焊接,把凸点间距继续降低到 10 微米以下大幅提高芯片互连密度和带宽,并降低电阻。Foveros Direct 还实现了功能单元分区,让模块化设计做到配置灵活、可定制。

先进封装为什么重要?

通过这次更新的制程路线图,我们不难看出英特尔非常重视先进封装。那么先进封装为什么重要?

虽然封装最开始的作用只是防水、防尘和散热,但随着制程技术逐渐逼近物理极限,它的地位已经完全不同。

为了满足越来越高、越来越复杂的算力需求,同时提高能效比,追求可持续发展,先进封装在芯片制造中的作用正变得越来越关键。先进封装技术一方面能够提升芯片互连密度,在单个封装中集成更多功能单元。另一方面,也将支持英特尔的产品部门和代工客户的异构集成需求,让来自不同供应商、用不同制程节点打造的芯粒(小型的模块化芯片)更好地协同工作,提高灵活性和性能,降低成本和功耗。目前英特尔的先进封装有两大支柱,分别是 EMIB 和 Foveros。

EMIB 简单来说就是把不同的芯片放在同一块平面上相互连接。传统的 2.5D 封装是在芯片和基板间的硅中介层上进行布线,EMIB 则是通过一个嵌入基板内部的单独的芯片完成互连,从而将芯片互连的凸点间距降低到 45 微米,改善了设计的简易性和成本。

Foveros 是英特尔的 3D 封装技术,在原理上同样并不复杂,就是在垂直层面一层一层地堆叠独立的模块,就像建高楼大厦一样。而高楼需要贯通的管道用于供电供水,Foveros 就是通过复杂的硅通孔技术实现垂直层面的互连。

产品方面

按照英特尔制程路线图上的时间表来看,英特尔会在 2025 年通过 Intel 18A“翻盘”。但是制程路线图上的时间表只是“工艺的时间表”,而不是产品落地的时间表。英特尔具体能否翻盘还是要看采用相关工艺的产品何时落地。

在消费级领域,英特尔于 2023 年 10 月发布了英特尔酷睿第 14 代台式机处理器。英特尔酷睿第 14 代处理器的“主要工艺”是 Intel 7。

英特尔于 2023 年 12 月发布了产品代号为 Meteor Lake 的英特尔酷睿 Ultra 处理器。英特尔酷睿 Ultra 处理器的“主要工艺”是 Intel 4。

而在服务器领域,英特尔于 2023 年 12 月发布了第五代英特尔至强可扩展处理器,第五代英特尔至强可扩展处理器的“主要工艺”是 Intel 7。

由此可见,工艺时间表和产品落地的时间表之间存在着一定的延迟。